# **JVC** SERVICE MANUAL

# COMPACT COMPONENT SYSTEM

# MX-J970V MX-J980V

This Illustration is MX-J980V

#### Each difference point

| Model    | CD/DECK/RECEIVER | SPEAKER    | Color        |                |            |                |

|----------|------------------|------------|--------------|----------------|------------|----------------|

|          |                  |            | Tray fitting | Panel          | Net        | Front          |

| MX-J970V | CA-MXJ970V       | SP-MXJ970V | Light gold   | Silver         | Light blue | Silver         |

| MX-J980V | CA-MXJ980V       | SP-MXJ980V |              | Champagne-gold | Gray       | Champagne-gold |

#### Contents

| Safety precautions 1-2            |

|-----------------------------------|

| Important for laser products 1-3  |

| Preventing static electricity 1-4 |

| Precautions at disassembling      |

| and parts replacement 1-5         |

| Disassembly method 1-6            |

| Adjustment method 1-31            |

|                                   |

| Diagnosis which uses             |

|----------------------------------|

| extension wire method 1-35       |

| Flow of functional operation     |

| until TOC read ······· 1-36      |

| Maintenance of laser pickup 1-37 |

| Replacement of laser pickup 1-37 |

| Description of major ICs 1-38    |

|                                  |

# -Safety Precautions -

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services should be performed by qualified personnel only.

- 2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product should not be made. Any design alterations or additions will void the manufacturer's warranty and will further relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

- 3. Many electrical and mechanical parts in the products have special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by (1) on the Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

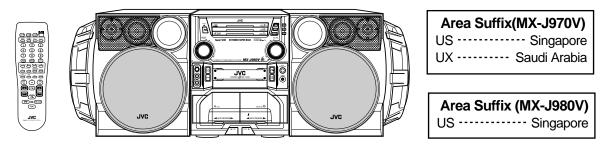

- 5. Leakage current check (Electrical shock hazard testing) After re-assembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the product is safe to operate without danger of electrical shock. Do not use a line isolation transformer during this check.

- Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.)

- Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having 1,000 ohms per volt or more sensitivity in the following manner. Connect a  $1,500\Omega$  10W resistor paralleled by

a  $0.15\mu$ F AC-type capacitor between an exposed metal part and a known good earth ground. Measure the AC voltage across the resistor with the AC voltmeter. Move the resistor connection to each exposed metal part, particularly any exposed metal part having a

return path to the chassis, and measure the AC voltage across the resistor. Now, reverse the plug in the AC outlet and repeat each measurement. Voltage measured any must not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

#### -Warning

- 1. This equipment has been designed and manufactured to meet international safety standards.

- 2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained. 3. Repairs must be made in accordance with the relevant safety standards.

- 4. It is essential that safety critical components are replaced by approved parts.

- 5. If mains voltage selector is provided, check setting for local voltage.

CAUTION Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

# Important for laser products

#### **1.CLASS 1 LASER PRODUCT**

- **2.DANGER :** Invisible laser radiation when open and inter lock failed or defeated. Avoid direct exposure to beam.

- **3.CAUTION :** There are no serviceable parts inside the Laser Unit. Do not disassemble the Laser Unit. Replace the complete Laser Unit if it malfunctions.

**4.CAUTION :** The compact disc player uses invisible laser radiation and is equipped with safety switches which prevent emission of radiation when the drawer is open and the safety interlocks have failed or are defeated. It is dangerous to defeat the safety switches.

- **5.CAUTION :** If safety switches malfunction, the laser is able to function.

- **6.CAUTION :** Use of controls, adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.

A CAUTION Please use enough caution not to see the beam directly or touch it in case of an adjustment or operation check.

- VARNING : Osynlig laserstrålning är denna del är öppnad och spårren är urkopplad. Betrakta ej strålen.

- VARO : Avattaessa ja suojalukitus ohitettaessa olet alttiina näkymättömälle lasersäteilylle.Älä katso säteeseen.

- ADVARSEL : Usynlig laserstråling ved åbning , når sikkerhedsafbrydere er ude af funktion. Undgå udsættelse for stråling.

ADVARSEL : Usynlig laserstråling ved åpning,når sikkerhetsbryteren er avslott. unngå utsettelse for stråling.

| REPRODUCTION AND POSITION OF LABELS |                                                                                                                       |                                                                                                                                |                                                                                                                  |                                                                                                                                         |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| WARNING LABEL                       |                                                                                                                       |                                                                                                                                |                                                                                                                  |                                                                                                                                         |  |

|                                     | DANGER : Invisible laser radiation<br>when open and interlock or<br>defeated.<br>AVOID DIRECT EXPOSURE TO<br>BEAM (e) | VARO : Avattaessa ja suojalukitus<br>ohitettaessa olet altitiina<br>näkymättömälle lasersäteilylle.Älä<br>katso säteeseen. (d) | VARNING : Osynlig laserstrålning är<br>denna del är öppnad och spårren är<br>urkopplad. Betrakta ej strålen. (s) | ADVARSEL :Usynlig laserstråling<br>ved åbning , når<br>sikkerhedsafbrydere er ude af<br>funktion. Undgå udsættelse for<br>stråling. (f) |  |

| CLASS 1<br>LASER PRODUCT            |                                                                                                                       |                                                                                                                                |                                                                                                                  |                                                                                                                                         |  |

# **Preventing static electricity**

### 1. Grounding to prevent damage by static electricity

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

#### 2. About the earth processing for the destruction prevention by static electricity

In the equipment which uses optical pick-up (laser diode), optical pick-up is destroyed by the static electricity of the work environment.

Be careful to use proper grounding in the area where repairs are being performed.

#### 2-1 Ground the workbench

Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over it before placing the traverse unit (optical pickup) on it.

#### 2-2 Ground yourself

Use an anti-static wrist strap to release any static electricity built up in your body.

#### 3. Handling the optical pickup

- 1. In order to maintain quality during transport and before installation, both sides of the laser diode on the replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition. (Refer to the text.)

- 2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power source can easily destroy the laser diode.

#### 4. Handling the traverse unit (optical pickup)

1. Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

- 2. Cut off the shorted part of the flexible cable using nippers, etc. after replacing the optical pickup. For specific details, refer to the replacement procedure in the text. Remove the anti-static pin when replacing the traverse unit. Be careful not to take too long a time when attaching it to the connector.

- 3. Handle the flexible cable carefully as it may break when subjected to strong force.

- 4. It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it

#### Attention when traverse unit is decomposed

# \*Please refer to "Disassembly method" in the text for pick-up and how to detach the CD traverse mechanism.

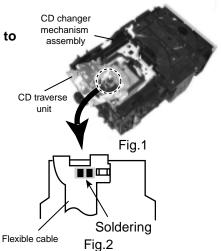

- 1. Remove the disk stopper and T. bracket on the CD changer mechanism assembly.

- 2. Disconnect the harness from connector on the CD motor board.

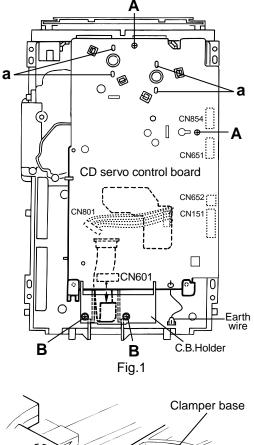

- 3. CD traverse unit is put up as shown in Fig.1.

- 4. Solder is put up before the card wire is removed from connector CN601 on the CD servo control board as shown in Fig. 2.

(When the wire is removed without putting up solder, the CD pick-up assembly might destroy.)

- 5. Please remove solder after connecting the card wire with CN601 when you install picking up in the substrate.

## Precautions at disassembling and parts replacement

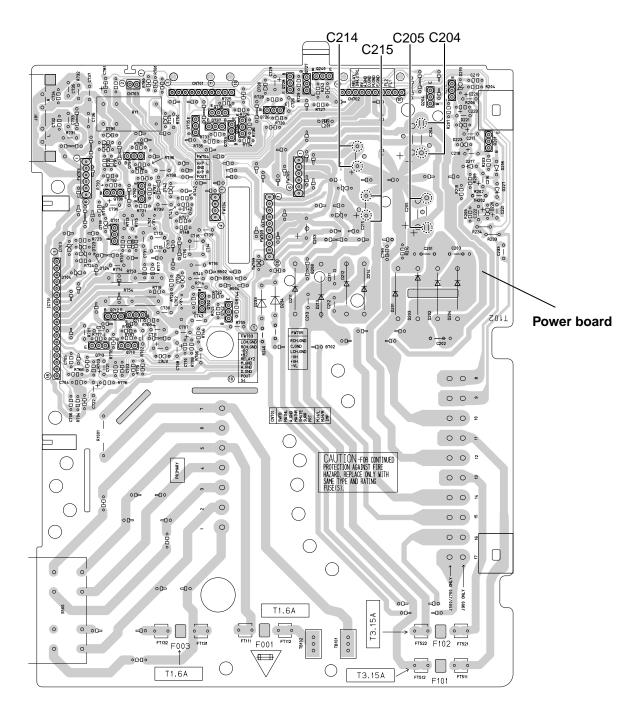

This model is charged with electricity on the power board even if the power cord is unplugged. Therefore, always discharge electricity in accordance with the steps given below before starting disassembling of the unit and/or replacement of parts.

- 1. While referring to the disassembling steps, remove the metal cover and the CD changer mechanism.

- Set electrical resistances of 1kohm, 1/4W to the places between the + and - terminals of condensers VH(C204, C205) and VL(C214, C215) on the power board, and discharge electricity for 4 ~ 5 seconds. Connection should be made at first for VH.

# **Disassembly method**

#### <Main body>

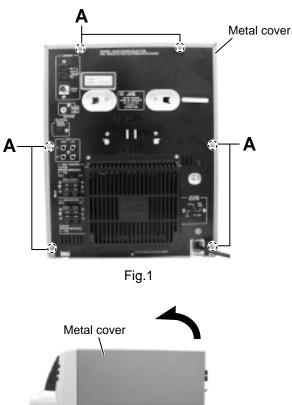

#### ■Removing the metal cover

(See Fig.1 to 3)

- 1. Remove the six screws **A** attaching the metal cover on the back of the body.

- 2. Remove the two screws **B** attaching the metal cover on both sides of the body.

- 3. Remove the metal cover from the body by lifting the rear part of the metal cover.

- ATTENTION: Do not break the front panel tab fitted to the metal cover.

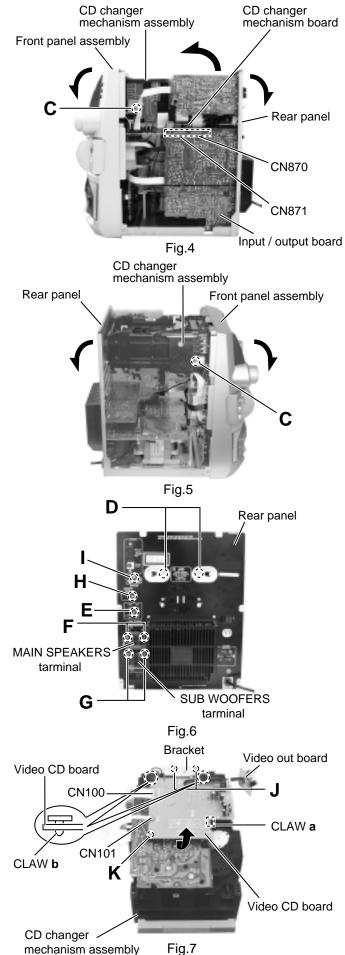

#### Removing the CD changer mechanism assembly (See Fig.4 to 6)

- Prior to performing the following procedure, remove the metal cover.

- 1. For the card wire connecting the CD changer mechanism board and the main board, disconnect it from connector CN868 on the main board.

- 2. Remove the two screws C attaching the CD changer mechanism assembly on both sides of the body.

- 3. Remove the two screws **D** attaching the CD changer mechanism assembly to the rear panel. Remove the screw E attaching the AUX terminal, two screws F attaching main speakers terminal and two screws G attaching the sub woofers terminal on the back of the body.

- 4. Remove the screw H attaching the CD optical digital output terminal on the back of the body.

- 5. Remove the screw I attaching the video out terminal on the back of the body.

- 6. Disconnect the harness from connector CN102 on the video CD board, and pull out the earth wire TW100 on the video CD board.

- 7. Pull the top of rear panel and the front panel assembly outward respectively, then remove the CD changer mechanism assembly by lifting the rear part of the CD changer mechanism assembly.

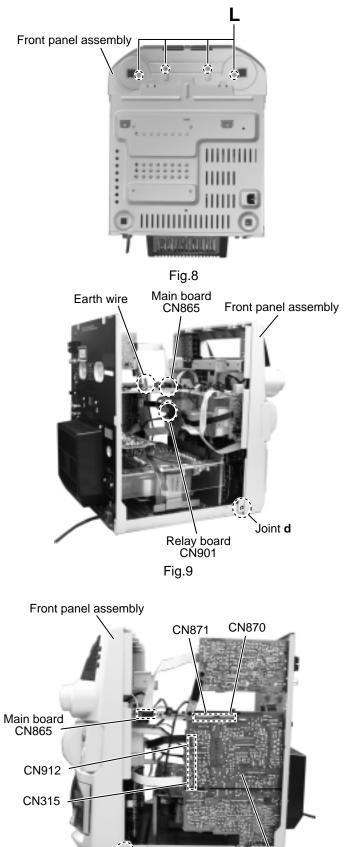

#### Removing the video CD board (See Fig.7)

- Prior to performing the following procedure, remove the CD changer mechanism assembly.

- 1. Reverse the CD changer mechanism assembly.

- 2. Remove the two screws J attaching the bracket.

- 3. Remove the screw K attaching the video CD board.

- 4. Disconnect the card wire from connector CN100 and CN101 on the video CD board.

- 5. At first, remove the claw a. Then remove the claw b while raising the video CD board in the direction of the arrow mark as figure. After removing the claw **b**, you can removing the video CD board by pulling it backward.

mechanism assembly

#### Removing the front panel assembly (See Fig.8 to 10)

- Prior to performing the following procedure, remove the metal cover and the CD changer mechanism assembly.

- 1. Remove the four screws L attaching the front panel assembly on the bottom of the body.

- 2. Disconnect the card wire from connector CN865 on the main board and pull out the earth wire on the main board.

- 3. Disconnect the card wire from connector CN315 on the input / output board.

- 4. Disconnect the harness from connector CN901 on the relay board on the back of the front panel assembly.

- 5. Disconnect the harness from connector CN912 on the input / output board.

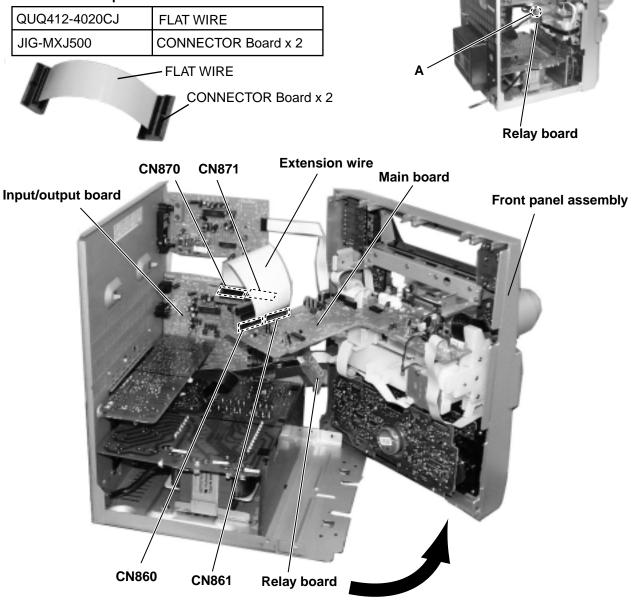

- 6. Disconnect connector CN870 and CN871 on the input/output board from the main board.

- 7. Release the two joints **c** and **d** on the lower part of the sides using a screwdriver, and remove the front panel assembly toward the front.

Fig.10

Input / output board

Joint c -

#### <Front panel assembly>

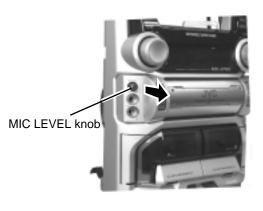

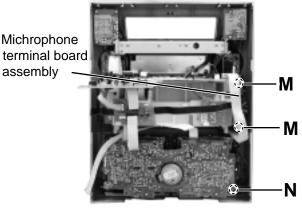

# Removing the Microphone terminal board assembly (See Fig.11 and 12)

- Prior to performing the following procedure, remove the metal cover, CD changer mechanism assembly and the front panel assembly.

- 1. Pull out the MIC level knob from the front side.

- 2. Remove the two screws  ${\bf M}$  attaching the microphone terminal board assembly.

- 3. Remove the screw  ${\bf N}$  attaching earth wire. Then release the earth wire from the clamp on the upper part of the cassette mechanism assembly.

- 4. Remove the michrophone terminal board assembly toward you.

Fig.11

Fig.12

Rolling panel assembly

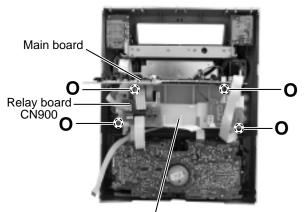

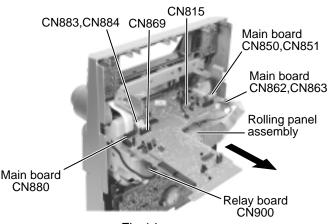

#### Removing the rolling panel assembly (See Fig.13 and 14)

- Prior to performing the following procedure, remove the michrophone terminal board assembly.

- 1. Disconnect the harness from connector CN900 on the relay board on the back of the rolling panel assembly.

- 2. Disconnect the harness from connector CN862, CN863, CN850, CN851 and CN815 on the main board respectively. Disconnect the card wire from connector CN880 on the main board.

- 3. Disconnect the card wire from connector CN869 and the harness from CN883 and CN884 on the main board respectively.

- 4. Remove the four screws **O** attaching the rolling panel assembly.

- ATTENTION: For the harness which should be connected to connector CN869, CN883 and CN884 on the main board, get them through the slots under the rolling panel when reattaching the rolling panel assembly to the front panel (Refer to Fig.14)

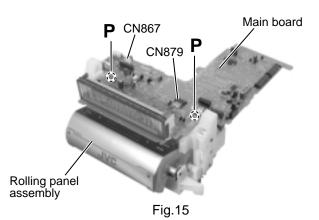

#### Removing the main board (See Fig.15 and 16)

- Prior to performing the following procedure, remove the front panel assembly, the microphone terminal board and the rolling panel assembly.

- 1. Disconnect the harness from connector CN867 on the main board.

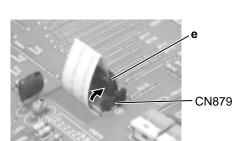

- 2. Disconnect the card wire from connector CN879 on the main board (Before pulling out the card wire, stand the part **e** of CN879 as shown in Fig.16).

- 3. Remove the two screws **P** attaching the main board.

Fig.16

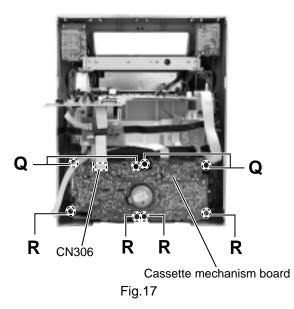

#### Removing the cassette mechanism assembly (See Fig.17)

- Prior to performing the following procedure, remove the front panel assembly.

- 1. Disconnect the card wire from connector CN306 on the cassette mechanism board.

- 2. Remove the eight screws **Q** and **R** attaching the cassette mechanism assembly.

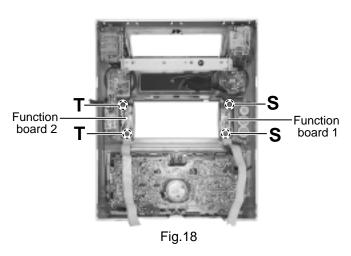

# Removing the boards in the front panel assembly (See Fig.18 to 20)

- Prior to performing the following procedure, remove the front panel assembly and the rolling panel assembly.

- Function board1 (See Fig.18)-

- 1. Remove the two screws **S** attaching the function board 1.

- Function board2 (See Fig.18) -

- 1. Remove the two screws **T** attaching the function board 2.

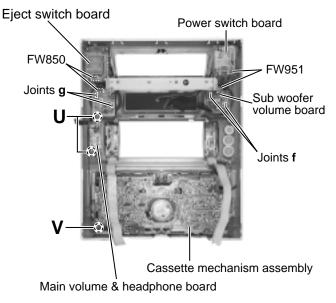

- Sub woofer volume board (See Fig.19) -

- 1. Pull out the sub woofer volume knob on the front side of the front panel assembly and remove the nut attaching the sub woofer volume board.

- 2. Release the two joints **f**. Unsolder FW951 on the sub woofer volume board and disconnect the harness connected to the power switch board.

- Main volume & headphone board (See Fig.19) -

- 1. Pull out the volume knob on the front side of the front panel assembly and remove the nut attaching the main volume & headphone board.

- 2. Remove the two screws **U** attaching the main volume & headphone board on the back of the front panel assembly and release the two joints **g**.

- 3. Unsolder FW850 on the main volume & headphone board and disconnect the harness connected to the eject switch board.

- 4. Remove the screw V attaching the earth wire extending from the main volume & headphone board.

Fig.19

#### MX-J970V/MX-J980V

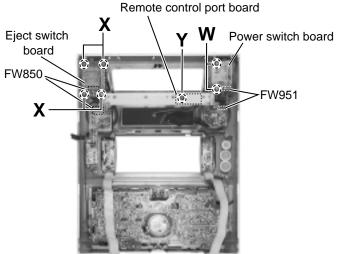

#### - Power switch board (See Fig.20) -

1. Remove the two screws **W** attaching the power switch board. Unsolder FW951 on the power switch board and disconnect the harness extending to the sub woofer volume board.

#### - Eject switch board (See Fig.20) -

1. Remove the four screws **X** attaching the eject switch board. Unsolder FW850 on the eject switch board and disconnect the harness extending to the main volume & headphone board.

#### - Remote control port board (See Fig.20) -

1. Remove the screw **Y** attaching the remote control port board.

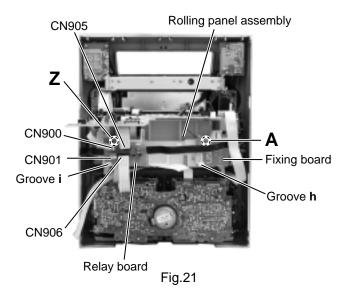

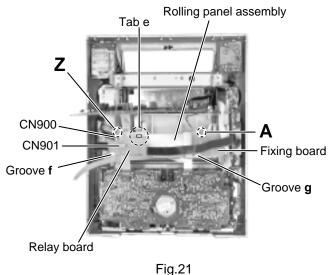

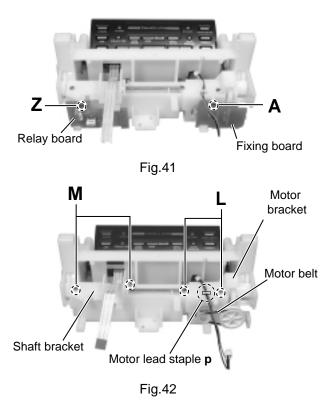

## Removing the relay board and fixing board (See Fig.21)

- Prior to performing the following procedure, remove the metal cover and CD changer mechanism assembly.

- There is no need to remove the front panel assembly.

- 1. Disconnect the harness from connector CN900 and CN901 and the card wire from connector CN905 and CN906 on the relay board on the back of the rolling panel assembly.

- 2. Remove the screw **Z** attaching the relay board and remove the relay board from the groove **i**.

- 3. Remove the screw **A** attaching the fixing board and remove the fixing board from the groove **h**.

Fig.20

### <Rear panel assembly>

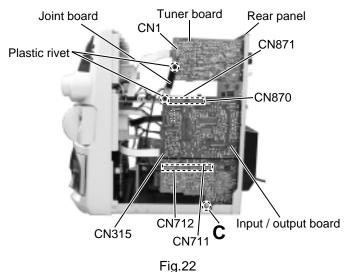

#### Removing the tuner board

(See Fig.22 and 23)

- Prior to performing the following procedure, remove the metal cover and the CD changer mechanism assembly.

- 1. Remove the two plastic rivets attaching the joint board, and remove the joint board.

- 2. Disconnect the card wire from connector CN1 on the tuner board.

- 3. Remove the two screws **B** attaching the tuner board on the back of the body.

#### Removing the input / output board (See Fig.22 and 23)

- Prior to performing the following procedure, remove the tuner board .

- 1. Disconnect the card wire from connector CN315 on the input / output board.

- 2. Remove the screw C attaching the input / output board on the lower side of the body.

- 3. Remove the five screws, E, F & G attaching the AUX, main speakers, sub woofers terminals board respectively on the back of the body.

- 4. Remove the screw **H** attaching the CD optical digital output terminal on the back of the body.

- 5. Disconnect the harness from connector CN912 on the input / output board and pull out the earth wire on the main board.

- 6. Disconnect connector CN870, CN871, CN612, CN711 and CN712 on the input / output board by pulling out them outward. Remove the input / output board from the body.

Fig.23

Rear panel

#### MX-J970V/MX-J980V

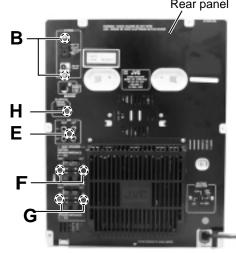

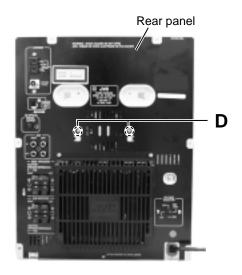

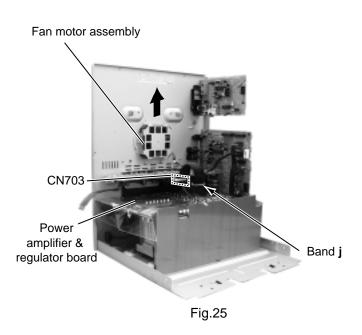

#### ■Removing the fan motor assembly (See Fig.24 and 25)

- Prior to performing the following procedure, remove the tuner board and input / output board.

- 1. Remove the two screws **D** attaching the fan motor assembly on the back of the body.

- 2. Cutoff the band **j** banding the harness.

- 3. Disconnect the harness from connector CN703 on the power amplifier & regulator board.

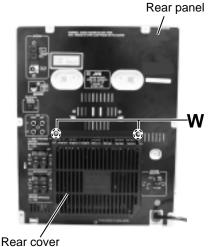

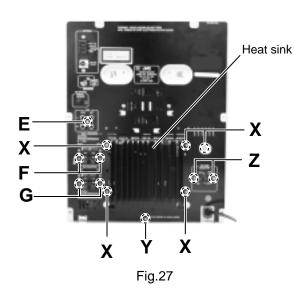

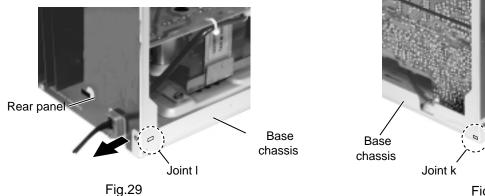

#### Removing the rear cover / rear panel (See Fig.26 to 29)

- Prior to performing the following procedure, remove the tuner board, input / output board and the fan motor assembly.

- There is no need to remove the front panel assembly.

- 1. Remove the two screws **W** attaching the rear cover on the back of the body.

- 2. Remove the five screws **E** & **F**, **G** attaching AUX, main speakers and sub woofers terminals to the rear panel on the back of the body.

- 3. Remove the five screws **X** attaching the heat sink and the preamplifier board to the rear panel on the back of the body.

- 4. Remove the two screws **Z** attaching the voltage selector terminal to the rear panel on the back of the body.

- 5. Remove the screw **Y** attaching the rear panel to the base chassis on the back of the body.

- 6. Release the two joints **k** and **l** on the rear panel bottom using a screwdriver, and detach the rear panel backward.

Fig.26

Base Joint k Fig.28

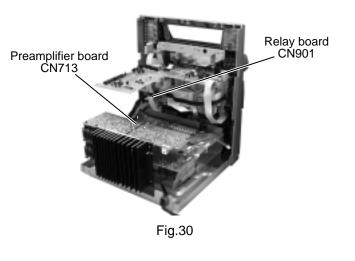

#### Removing the preamplifier board / heat sink (See Fig.30 to 32)

- Prior to performing the following procedure, remove the tuner board, input / output board the fan motor assembly and the rear cover / rear panel.

- There is no need to remove the front panel assembly.

- 1. Disconnect the harness from connector CN901 on the relay board on the back of the rolling panel assembly.

- 2. Disconnect the harness from connector CN713 on the preamplifier board.

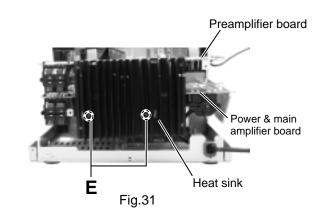

- 3. Remove the two screws **E** attaching the heat sink to the power & main amplifier board on the back of the body.

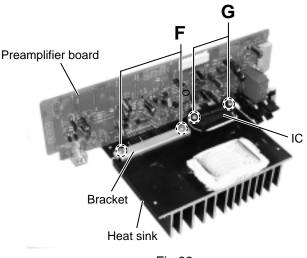

- 4. Remove the two screws  ${\bf F}$  &  ${\bf G}$  attaching the bracket and IC to the heat sink.

- 5. Remove the bracket, then detach the preamplifier board from the heat sink.

Fig.32

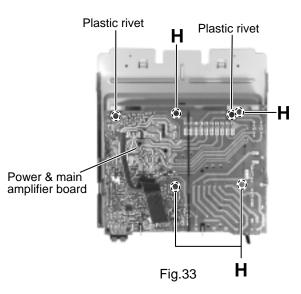

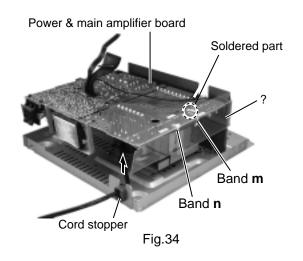

#### Removing the power & main amplifier board (See Fig.33 and 34)

- Prior to performing the following procedure, remove the metal cover, the CD changer mechanism assembly, the front panel assembly, the rear cover / rear panel, the tuner board, the input & output board and the preamplifier board.

- 1. Remove the four screws **H** attaching the transf. on the power & main amplifier board through the upper side slots.

- 2. Remove the two plastic rivets fixing the power & main amplifier board.

- 3. Remove the cord stopper by pushing it upward.

- 4. Cut off the bands **m** and **n** fixing the power cord and ?, and unsolder the power cord on the power & main amplifier board.

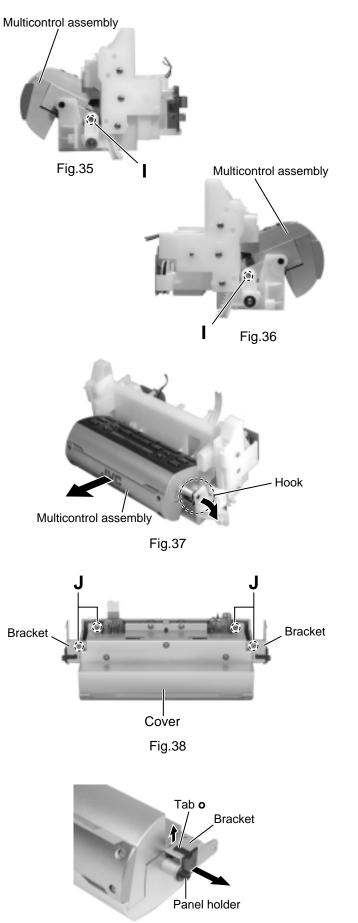

#### <Rolling panel assembly> Removing the multicontrol assembly (See Fig.35 to 37)

- Prior to performing the following procedure, remove the rolling panel assembly and the main board.

- 1. Remove the two screws I attaching the multicontrol assembly on both sides.

- 2. Remove the multicontrol assembly outward while pushing the right and left hooks fixing multicontrol assembly outward respectively.

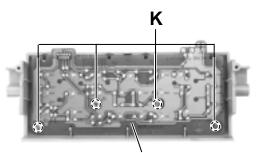

#### Removing the multicontrol board (See Fig.38 to 40)

- Prior to performing the following procedure, remove the rolling panel assembly, the main board and the multicontrol assembly.

- 1. Remove the four screws **J** attaching the cover and the bracket.

- 2. Pull out the right and left panel holders outward respectively by releasing the tabs **o** outward.

- 3. Remove the cover and the bracket.

- 4. Remove the four screws  ${\bf K}$  attaching the multicontrol board.

Multicontrol board

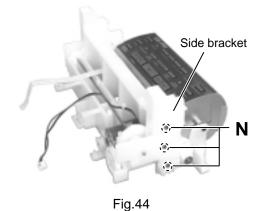

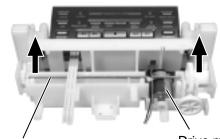

#### ■Removing the drive motor assembly (See Fig.41 to 44)

- Prior to performing the following procedure, remove the rolling panel assembly and the main board assembly.

- 1. Remove the relay board and fixing board (Refer to Fig.21).

- 2. Remove the two screws L attaching the motor bracket and remove the motor lead staple **p**.

- 3. Remove the two screws  ${\bf M}$  attaching the shaft bracket.

- 4. Remove the motor belt.

- 5. Remove the three screws **N** attaching the side bracket.

- 6. Remove the shaft assembly from the rolling panel assembly by life up the shaft assembly upward.

Shaft assembly

Drive motor

#### < Speaker section >

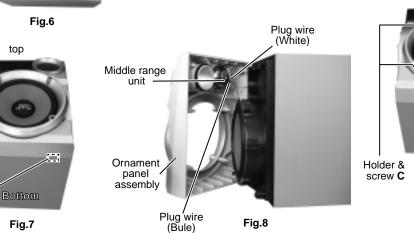

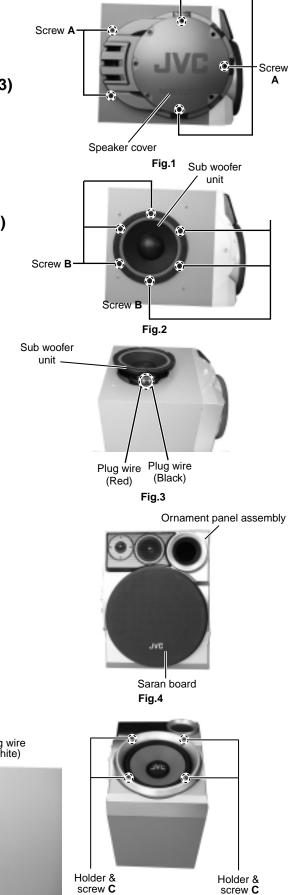

#### Removing the speaker cover (See Fig.1)

1. Remove the five screws **A** attaching the speaker cover on the side of the body.

#### Removing the sub woofer unit (See Fig.2 and 3)

- 1. Remove the six screws **B** attaching the sub woofer unit.

- 2. Two plug wires connected with the sub woofer unit are pulled out.

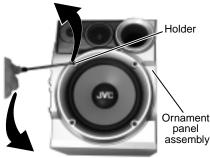

#### Removing the ornament panel assembly (See Fig.4 to 8)

- Remove the saran board from the speaker box. (Saran board can be detached by pulling the speaker cover forward.)

- 2. The plus driver is inserted in the holder, it is lifted, and the holder is removed.

- 3. Four holders are removed, and four screws **C** under that are removed.

- The minus driver is inserted in the concave part in the speaker box bottom and inserts in the interior little by little.

- CAUTION : Please apply the felt or the cloth, etc. to damage neither the ornament panel nor the cabinet when the ornament panel assembly is detached when working.

- 5. Two plug wires connected with the middle range unit are pulled out.

Fig.5

concave part

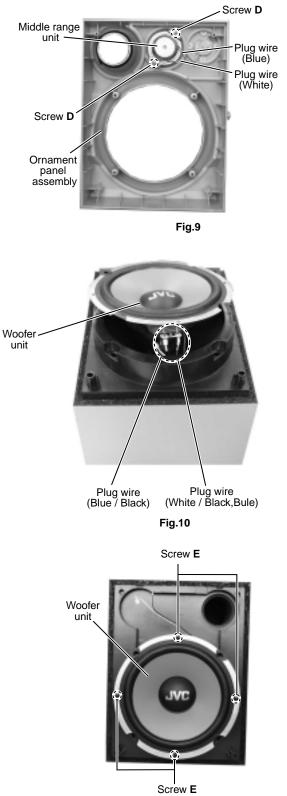

#### Removing the middle range unit (See Fig.9)

- 1. Remove the ornament panel assembly.

- 2. Remove the two screws **D** attaching the middle range unit.

- 3. Two plug wires connected with the middle range unit are pulled out.

#### ■ Removing the woofer unit (See Fig.10 and 11)

- 1. Remove the ornament panel assembly.

- 2. Remove the four screws E attaching the woofer unit.

- 3. Two plug wires connected with the woofer unit are pulled out.

≪CD Changer Mechanism Type:VC3 Section≫

#### Removing the CD Servo control board (See Fig.1)

- 2.Remove the CD changer mechanism assembly.

- From bottom side the CD changer mechanism assembly, remove the two screws A retaining the CD servo control board.

- 4.Absorb the four soldered positions "a" of the right and left motors with a soldering absorber.

- 5.Pull out the earth wire on the CD changer mechanism assembly.

- 6.The two screws **B** is removed and C.B.holder is detached.

- 7.Disconnect the connector CN854 on the CD servo control board.

- 8.Disconnect the card wire CN601 and the connector CN801 on the CD servo control board.

### ■ Removing the CD tray assembly

- 1. Remove the front panel assembly. (See Fig.2~4)

- 2. Remove the CD changer mechanism assembly.

- 3. Remove the CD Servo control board.

- 4. Remove the screw C' retaining the lod stopper.

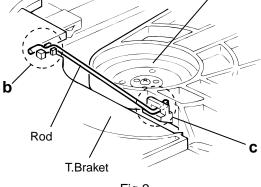

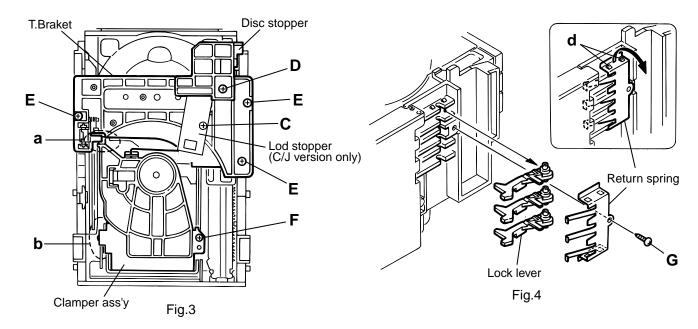

- 5. From the T.bracket section "b" and clamper base section "c", remove both of the edges fixing the rod(See Fig.2 and 3).

- 6. Remove the screw  $\, {\bf D} \,$  retaining the disc stopper

- (See Fig.3). 7. Remove the three screws **E** retaining the T.bracket

- (See Fig.3). 8. Remove the screw **F** retaining the clamper assembly (See Fig.3).

- 9. From the left side face of the chassis assembly, remove the one screw **G** retaining both of the return spring and lock lever(See Fig. 4).

- 10.By removing the pawl at the section "d" fixing the return spring, dismount the return spring(See Fig.4).

- 11. Remove the three lock levers(See Fig.4).

#### MX-J970V/MX-J980V

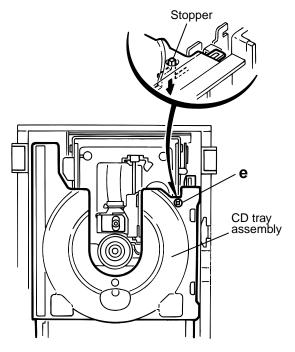

- 11. Check whether the lifter unit stopper has been caught into the hole at the section "e" of CD tray assembly as shown in Fig.5.

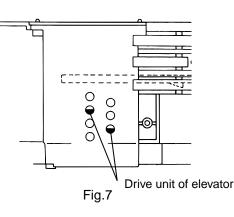

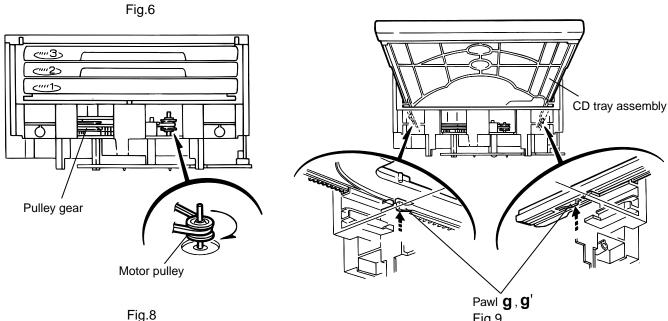

- 12. Make sure that the driver unit elevator is positioned as shown in Fig.6 from to the second or fifth hole on the left side face of the CD changer mechanism assembly.

- [Caution] In case the driver unit elevator is not at above position, set the elevator to the position as shown in Fig.7 by manually turning the pulley gear as shown in Fig.8.

- 13. Manually turn the motor pulley in the clockwise direction until the lifter unit stopper is lowered from the section "e" of CD tray assembly(See Fig.8).

- 14. Pull out all of the three stages of CD tray assembly in the arrow direction "f" until these stages stop

- (See Fig.6).

CD tray assembly

15. At the position where the CD tray assembly has stopped, pull out the CD tray assembly while pressing the two pawls "g and g' " on the back side of CD tray assembly(See Fig.9). In this case, it is easy to pull out the assembly when it is pulled out first from the stage CD tray assembly.

Pawl g

Chassis assembly

° 0 00

Refer to Fig.7

Fig.5

Fig.9

#### Removing the CD loading mechanism assembly(See Fig.10)

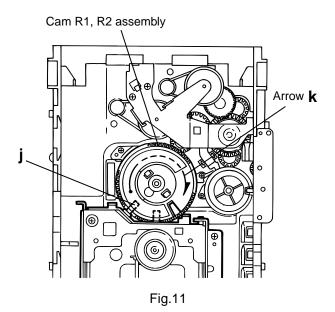

- 1. While turning the cams R1 and R2 assembly in the arrow direction "h" ,align the shaft "i" of the CD loading mechanism assembly to the position shown in Fig.10.

- 2. Remove the four screws **H** retaining the CD loading mechanism assembly.

#### Removing the CD traverse mechanism (See Fig.11 and 12)

- 1. For dismounting only the CD traverse mechanism without removing the CD loading mechanism assembly, align the shaft "j" of the CD loading mechanism assembly to the position shown Fig.11 while turning the cam R1 and R2 assembly in the arrow direction "k".

- 2. By raising the CD loading mechanism assembly in the arrow direction "I", remove the assembly from the lifter unit

#### Removing the CD pick unit (See Fig.13)

- 1. Move the cam gear in the arrow direction "m" . Then, the CD pickup unit will be moved in the arrow direction "n" .

- 2. According to the above step, shift the CD pickup unit to the center position.

- 3. While pressing the stopper retaining the shaft in the arrow direction "o", pull out the shaft in the arrow direction "p".

- 4. After dismounting the shaft from the CD pickup unit, remove the CD pickup unit

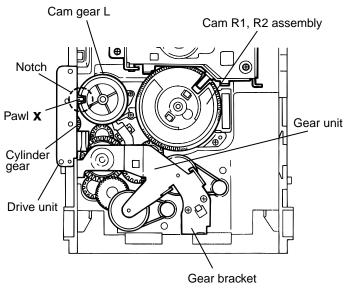

# Removing the cam unit

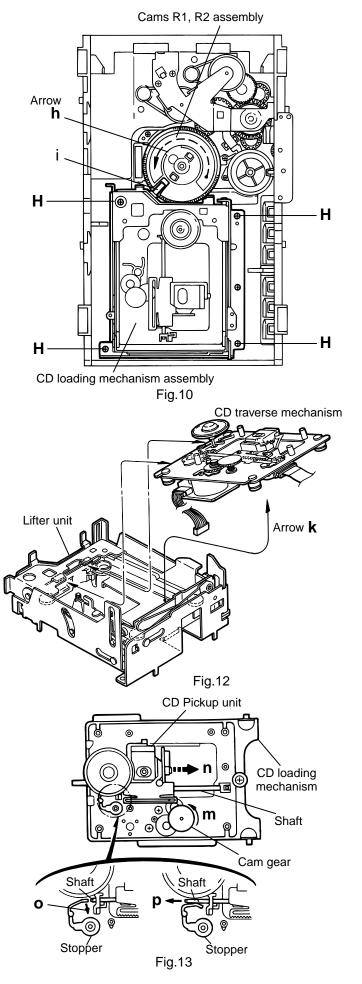

- (See Fig.14 ~17)

- 1. Remove the CD loading mechanism assembly.

2. While turning the cam gear "q", align the pawl "r" position of the drive unit to the notch position(Fig.16) on the cam gear "q".

- 3. Pull out the drive unit and cylinder gear(See Fig.17).

- 4. While turning the cam gear "q", align the pawl "s" position of the select lever to the notch position(Fig.18) on the cam gear "q".

- 5. Remove the four screws **J** retaining the cam unit(cam gear "q" and cams R1/R2 assembly)(See Fig.18).

Fig.17

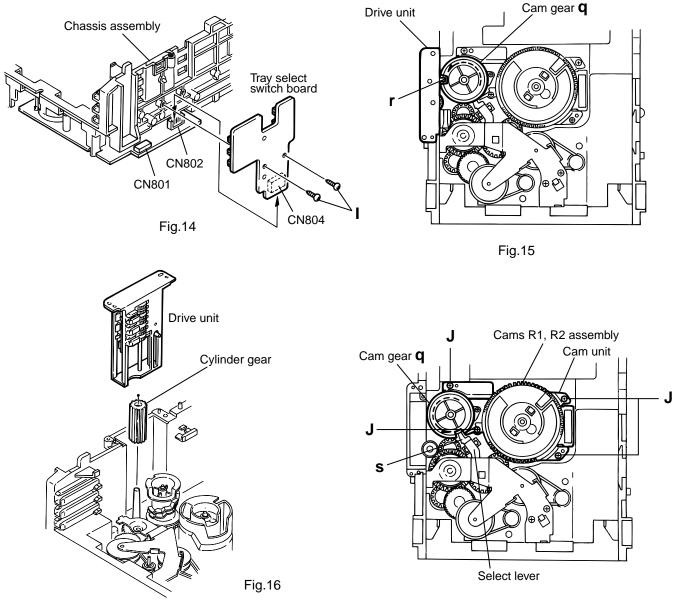

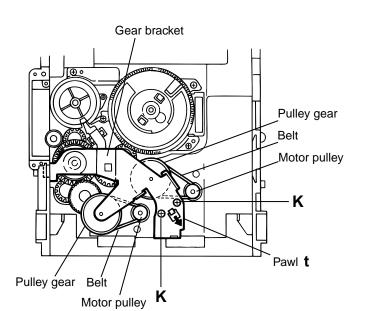

#### ■ Removing the actuator motor and belt (See Fig.18~21)

- 1. Remove the two screws **K** retaining the gear bracket (See Fig.19).

- 2. While pressing the pawl "t" fixing the gear bracket in the arrow direction, remove the gear bracket

(See Fig.19).

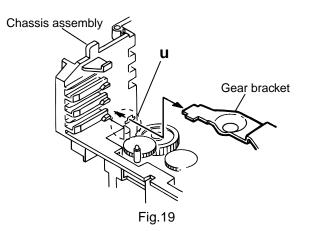

- 3. From the notch "u section" on the chassis assembly fixing the edge of gear bracket, remove and take out the gear bracket(See Fig. 20).

- 4. Remove the belts respectively from the right and left actuator motor pulleys and pulley gears(See Fig. 19).

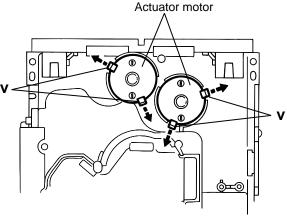

- 5. After turning over the chassis assembly, remove the actuator motor while spreading the four pawls "v" fixing the right and left actuator motors in the arrow direction(See Fig. 21).

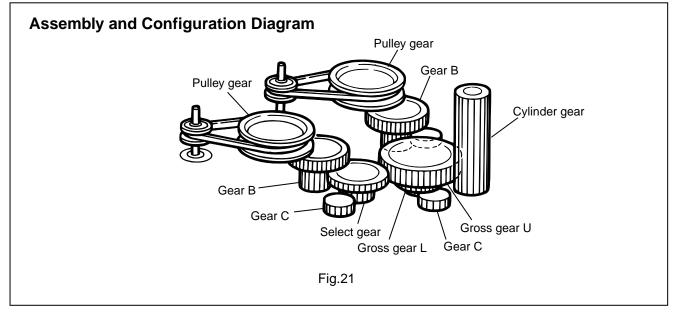

- **[Note]** When the chassis assembly is turned over under the conditions wherein the gear bracket and belt have been removed, then the pulley gear as well as the gear, etc. constituting the gear unit can possibly be separated to pieces. In such a case, assemble these parts by referring to the assembly and configuration diagram in Fig. 22.

Fig.18

Fig.20

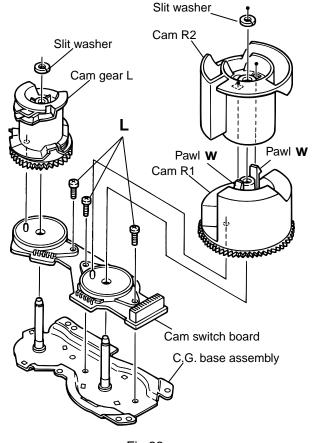

#### Removing the cams R1/R2 assembly and cam gear q(See Fig.22)

- 1. Remove the slit washer fixing the cams R1 and R2 assembly.

- 2. By removing the two pawls "w" fixing the cam R1, separate R2 from R1.

- 3. Remove the slit washer fixing the cam gear "q".

- 4. Pull out the cam gear "q" from the C.G. base assembly.

#### Removing the C.G. base assembly (See Fig.22 and 23)

Remove the three screws L retaining the C.G. base assembly.

[Caution] To reassemble the cylinder gear, etc.with the cam unit (cam gear and cans R1/R2 assembly), gear unit and drive unit, align the position of the pawl "x" on the drive unit to that of the notch on the cam gear "q". Then, make sure that the gear unit is engaged by turning the cam gear "q" (See Fig. 24).

Fig.23

#### < Cassette mechanism section >

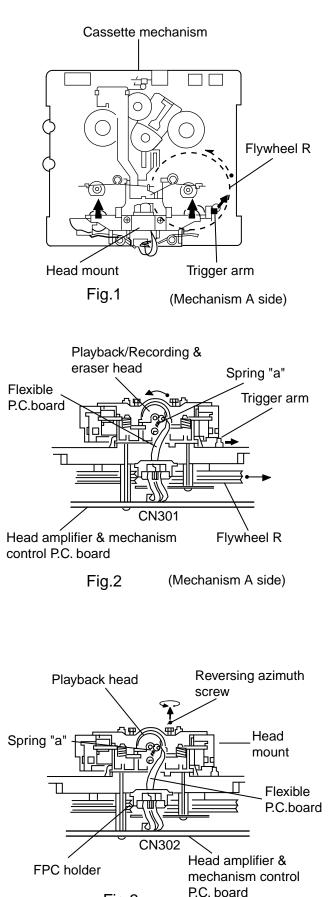

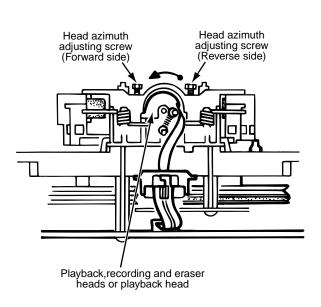

#### Removing the playback, recording and eraser heads (See Fig.1~3)

- 1. While shifting the trigger arms seen on the right side of the head mount in the arrow direction,turn the flywheel R in counterclockwise direction until the head mount has gone out with a click (See Fig. 1).

- 2. When the flywheel R is rotated in counterclockwise direction, the playback head will be turned in counterclockwise direction from the position in Fig.2 to that in Fig.3.

- 3. At this position, disconnect the flexible P.C.board (outgoing from the playback head) from the connector CN301 on the head amp. and mechanism control P.C. board.

- 4. After dismounting the FPC holder, remove the flexible P.C.board.

- 5. Remove the flexible P.C.board from the chassis base.

- 6. Remove the spring "a" from behind the playback head.

- 7. Loosen the reversing azimuth screw retaining the playback head.

- 8. Take out the playback head from the front of the head mount.

- 9. The recording and eraser heads should also be removed similarly according to Steps 1~8 above.

# Reassembling the playback, recording and eraser heads (See Fig.2,3)

- 1. Reassemble the playback head from the front of the head mount to the position as shown in Fig.3.

- 2. Fix the reversing azimuth screw.

- 3. Set the spring a from behind the playback head.

- 4. Attach the flexible P.C.board to the chassis base, and fix it with the FPC holder as shown in Fig.3.

- 5. The recording and eraser heads should also be reassembled similarly according to Steps 1~4 above.

Fig.3

(Mechanism B side)

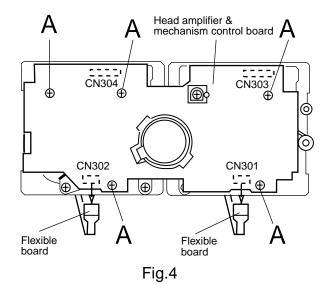

#### Removing the head amp.and mechanism control P.C.board (See Fig. 4)

- 1.Remove the cassette mechanism assembly.

- 2.After turning over the cassette mechanism assembly,remove the five screws "A" retaining the head amp. and mechanism control P.C. board

- 3.Disconnect the connectors CN303 and CN304 on the P.C.Board and the connectors CN1 on both the right and left side reel pulse P.C.Boards.

- 4.When necessary, remove the 4pin parallel wire soldered to the main motor

■ Removing the capstan motor assembly

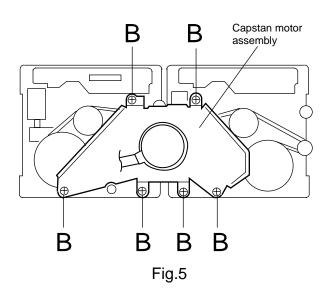

- 1.Remove the six screws "B" retaining capstan motor assembly (See Fig. 5).

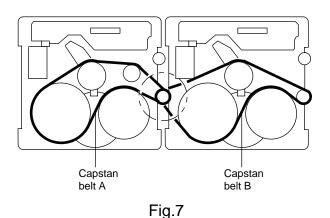

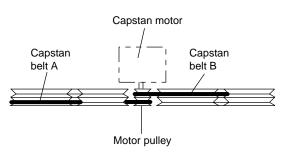

- 2.While raising the capstan motor, remove the capstan belts A and B respectively from the motor pulley (See Fig. 6).

- Caution 1: Be sure to handle the capstan belts so carefully that these belts will not be stained by grease and other foreign matter. Moreover, these belts should be hand while referring to the capstan belt hanging method.

Fig.6

#### Removing the capstan motor (See Fig. 8)

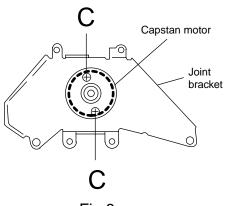

From the joint bracket, remove the two screws "C" retaining the capstan motor.

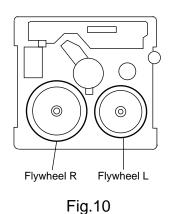

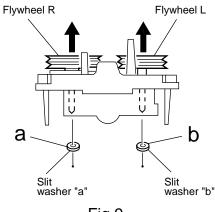

#### Removing the flywheel (See Fig. 9,10)

- 1.Remove the head amp. and mechanism control P.C.Board.

- 2.Remove the capstan motor assembly.

- 3.After turning over the cassette mechanism, remove the slit washers "a" and "b" fixing the capstan shafts R and L, and pull out the flywheels R and L respectively from behind the cassette mechanism.

Fig.9

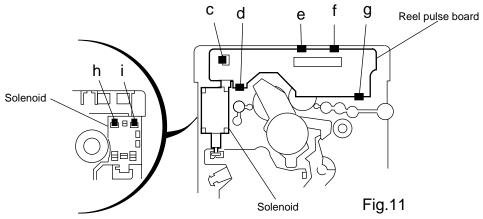

# ■ Removing the reel pulse P.C.board and solenoid (See Fig. 11)

- 1.Remove the five pawls (c,d,e,f,g) retaining the reel pulse P.C.Board.

- 2.From the surface of the reel pulse P.C.Board parts, remove the two pawls "h" and "i" retaining the solenoid.

# Adjustment method

#### Measurement instruments required for adjustment

- Low frequency oscillator, This oscillator should have a capacity to output 0dBs to 600ohm at an oscillation frequency of 50Hz-20kHz.

- 2. Attenuator impedance : 600ohm

- 3. Electronic voltmeter

- 4. Frequency counter

- 5. Wow flutter meter

- 6. Test tape

VTT712 : For Tape speed and wow flutter (3kHz) VTT724 : For Reference level (1kHz)

TMT7036 : For Head angle(10kHz),Play back frequency characteristics(1kHz),and dubbing frequency characteristics(63,1,10kHz)

Because of frequency-mixed tape with 63,1k,10k and 14kHz(250nWb/m -24dB).

Use this tape together with a filter.

7. Blank tape

TAPE I: AC-225, TAPE II: AC-514

- 8. Torque gauge : For play and back tension Forward ; TW2111A, Reverse ; TW2121A Fast Forward and Rewind ; TW2231A

- 9. Test disc

- : CTS-1000(12cm),GRG-1211(8cm)

10. Jitter meter

#### **Measurement conditions**

Power supply voltage AC110/127/220-240V(50/60Hz)

#### Measurement

output terminal : Speaker out :TP101(Mesuring for TUNER/DECK/CD) :Dummy load 60hm

#### Radio input signal

AM modulation frequency : 400Hz Modulation factor : 30% FM modulation frequency : 400Hz Frequency displacement : 22.5kHz

#### **Frequency Range**

| AM | 531kHz~1710kHz |

|----|----------------|

|    | 531kHz~1602kHz |

| FM | 87.5MHz~108MHz |

# Standard measurement positions of volume and switch

Power : Standby (Light STANDBY Indicator) S,A,BASS : OFF Sound mode : OFF Main VOL. : 0 Minimum Travers mecha set position : Disc 1 Mic MIX vol : MAX ECHO : OFF

#### **Precautions for measurement**

- 1. Apply 30pF and 33kohm to the IF sweeper output side and 0.082 F and 100kohm in series to the sweeper input side.

- 2. The IF sweeper output level should be made as low as possible within the adjustable range.

- 3. Since the IF sweeper is a fixed device, there is no need to adjust this sweeper.

- 4. Since a ceramic oscillator is used, there is no need to perform any MPX adjustment.

- 5. Since a fixed coil is used, there is no need to adjust the FM tracking.

- 6. The input and output earth systems are separated. In case of simultaneously measuring the voltage in both of the input and output systems with an electronic voltmeter for two channels, therefore, the earth should be connected particularly.

- 7. In the case of BTL connection amplifier, the minus terminal of speaker is not for earthing. Therefore, be sure not to connect any other earth terminal to this terminal. This system is of an OTL system.

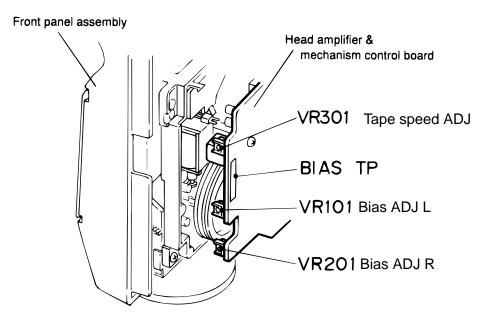

#### ■ Arrangement of adjusting positions

Head azimuth adjusting screw (Forward side)

Cassette mechanism section (Mechanism A section)

# Cassette mechanism section (Back side)

Cassette Mechanism Unit Section

### ■ Tape recorder section

| Items                         | Measurement conditions                                                                                                                        | Measurement method                                                                                                                                                                                                                                                                                                                                                                                                                       | Standard values                                          | Adjusting positions                                                            |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------|

| Confirmation<br>of head angle | Test tape<br>:TMT7036(10kHz)<br>Measurement<br>output terminal<br>:Speaker terminal<br>Speaker R<br>(Load resistor:3Ω)<br>:Headphone terminal | <ol> <li>Playback the test tape TMT7036(10kHz).</li> <li>With the playback mechanism or recording &amp; playback mechanism, adjust the head azimuth screw so that the forward and reverse output levels become maximum. After adjustment, lock the head azimuth at least by half a turn.</li> <li>In either case, this adjustment should be performed in both the forward and reverse directions with the head azimuth screw.</li> </ol> | Maximum<br>output                                        | Adjust the head<br>azimuth screw<br>only when the<br>head has been<br>changed. |

| Confirmation<br>of tape speed | Test tape<br>:VTT712(3kHz) or<br>TMT7036(3kHz)<br>Measurement<br>output terminal<br>:Headphone terminal                                       | <constant speed=""><br/>Adjust VR301 so that the frequency counter reading<br/>becomes 3,000Hz±60Hz when playing back the<br/>test tape VTT712(3kHz)with the playback mechanism<br/>or playback and recording mechanism after ending<br/>forward winding of the tape.</constant>                                                                                                                                                         | Tape speed<br>of decks<br>(A and B)<br>:3,000Hz<br>±60Hz | VR301                                                                          |

#### Reference values for confirmation items

| Items                                                                                           | Measurement conditions                                                                                                                                                    | Measurement method                                                                                                                                                                                                                                                               | Standard values              | Adjusting positions                                           |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------------------------------|

| Double tape<br>speed                                                                            | Test tape<br>:VTT712<br>Measurement<br>output terminal<br>:Speaker terminal<br>Speaker R<br>(Load resistance:3Ω)<br>measurement<br>output terminal<br>:Headphone terminal | After setting to the double speed motor, confirm<br>that the frequency counter reading becomes<br>4,800+400/-300Hz when the test tape VTT712<br>(3kHz) has been play back with the playback<br>mechanism.                                                                        | 4,800+400/<br>-300Hz         | Playback<br>mechanism side                                    |

| Difference<br>between the<br>forward and<br>reverse speed.<br>P.mecha and<br>R/P mecha<br>speed |                                                                                                                                                                           | When the test tape VTT712(3kHz) has been played<br>back with the playback mechanism or recording and<br>playback mechanism at the beginning of forward<br>winding, the frequency counter reading of the<br>difference between both of the mechanisms should<br>be 6.0Hz or less. | 60Hz or<br>less              | Both the playback<br>and recording &<br>playback<br>mechanism |

| Wow & flutter                                                                                   | Test tape<br>:VTT712<br>Measurement<br>output terminal<br>:Headphone terminal                                                                                             | When the test tape VTT712(3kHz) has been played back with the playback mechanism or recording and playback mechanism at the beginning of forward winding the frequency counter reading of wow & flutter should be 0.25% or less(WRMS).                                           | with in<br>0.25%<br>JIS(WTD) | Both the playback<br>and recording &<br>playback<br>mechanism |

### Electrical performance

| Items                                                                      | Measurement conditions                                                                                                                                                    | Measurement method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Standard values                                                 | Adjusting positions            |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------|

| Adjustment of<br>recording bias<br>current<br>(Reference<br>value)         | *Mode : Forward or<br>reverse mode<br>*Recording mode<br>*Test tape<br>:AC-514 and AC-225<br>Measurement output<br>terminal<br>:Both recording and<br>headphone terminals | <ol> <li>With the recording and playback mechanism,<br/>load the test tapes(AC-514 to TYP II and AC-225 to<br/>TYP I),and set the mechanism to the recording and<br/>pausing conditions in advance.</li> <li>After connecting 100 Ω in series to the recorder<br/>head,measure the bias current with a valve<br/>voltmeter at both of the terminals.</li> <li>After resetting the [PAUSE] mode,start recording.<br/>At this time,adjust VR101 for LcH and VR201 for<br/>RcH so that the recording bias current values<br/>become 4.0 µA (TYP I) and 4.20 µA(TYP II).</li> </ol> | AC-225<br>:4.20 μA<br>AC-514<br>:4.0 μA                         | LcH<br>:VR101<br>RcH<br>:VR201 |

| Adjustment of<br>recording and<br>playback<br>frequency<br>characteristics | Reference frequency<br>:1kHz and 10kHz<br>(REF:-20dB)<br>Test tape<br>:TYP II AC-514<br>Measurement input<br>terminal<br>:OSC IN                                          | <ol> <li>With the recording and playback mechanism,load<br/>the test tape(AC-514 to TYP II),and set the<br/>mechanism to the recording and pausing condition<br/>in advance.</li> <li>While repetitively inputting the reference frequency<br/>signal of 1kHz and 10kHz from OSC IN, record and<br/>playback the test tape.</li> <li>While recording and playing back the test tape in<br/>TYPII,adjust VR101 for LcH and VR201 for RcH<br/>so that the output deviation between 1kHz and<br/>10kHz becomes -1dB±2dB.</li> </ol>                                                | Output<br>deviation<br>between<br>1kHz and<br>10kH<br>:-1dB±2dB | LcH<br>:VR101<br>RcH<br>:VR201 |

#### ■ Reference values for electrical function confirmation items

| Items                                  | Measurement conditions                                                                                                                                             | Measurement method                                                                                                                                                                                                                                                                                                                                                                                                                  | Standard values                    | Adjusting positions |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------|

| Recording<br>bias frequency            | *Recording and<br>playback side forward<br>or reverse<br>*Test tape<br>:TYP II AC-514<br>*Measurement<br>terminal BIAS TP on<br>P.C.board                          | <ol> <li>While changing over to and from BIAS 1 and 2,<br/>confirm that the frequency is changed.</li> <li>With the recording and playback mechanism.<br/>load the test tape (AC-514 to TYPII),and set the<br/>mechanism to the recording and pausing<br/>conditions in advance.</li> <li>Confirm that the BIAS TP frequency on the<br/>P.C.board is 100kHz±6kHz.</li> </ol>                                                        | 100kHz<br>+9kHz<br>-7kHz           |                     |

| Eraser current<br>(Reference<br>value) | *Recording and<br>playback side forward<br>or reverse<br>*Recording mode<br>*Test tape<br>:AC-514 and AC-225<br>Measurement terminal<br>Both of the eraser<br>head | <ol> <li>With the recording and playback mechanism,<br/>load the test tapes(AC-514 to TYP II and AC-225<br/>to TYP I),and set the mechanism to the recording<br/>and pausing condition in advance.</li> <li>After setting to the recording conditions,connect<br/>1MΩ in series to the eraser head on the recording<br/>and playback mechanism side,and measure the<br/>eraser current from both of the eraser terminal.</li> </ol> | TYP II<br>:120mA<br>TYP I<br>:75mA |                     |

# Diagnosis which uses extension wire method

#### System control P.C.board

- 1.Remove the metal cover and CD changer mechanism.

- 2.Remove the front panel assembly.

- 3.One screw A is removed, and relay board is removed.

- 4.As shown in fig.1, place the front panel assembly after opening it outward using the right side of the front panel as an axis.

- 5.The extension wire is connected with CN870 & CN871 on the INPUT/OUTPUT board and CN860 & CN861 on the main board.

#### Extension wire parts No.

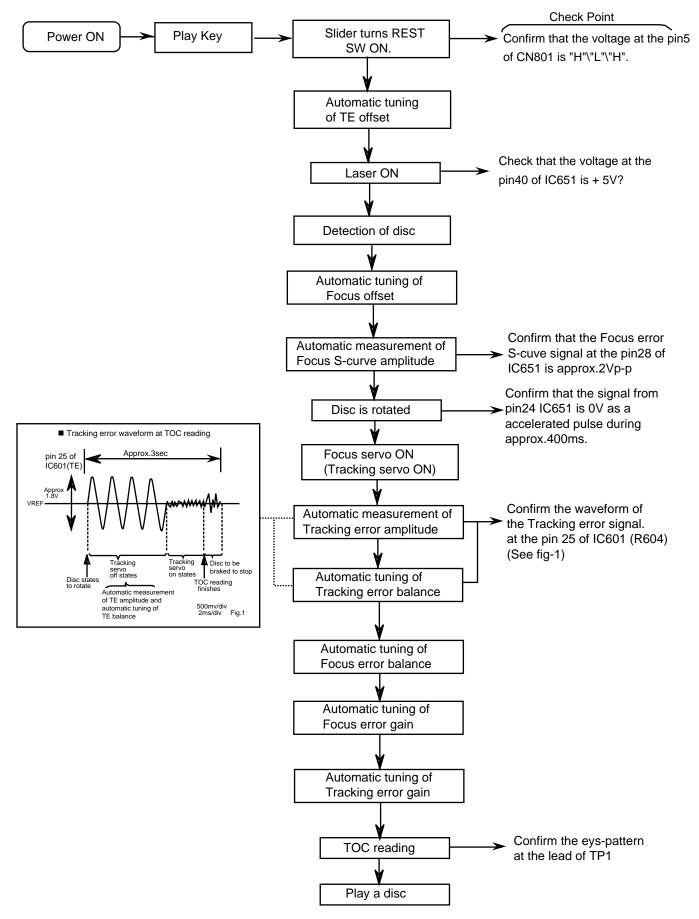

# Flow of functional operation until TOC read

**Replacement of laser pickup**

Turn off the power switch and, disconnect the

power cord from the ac outlet.

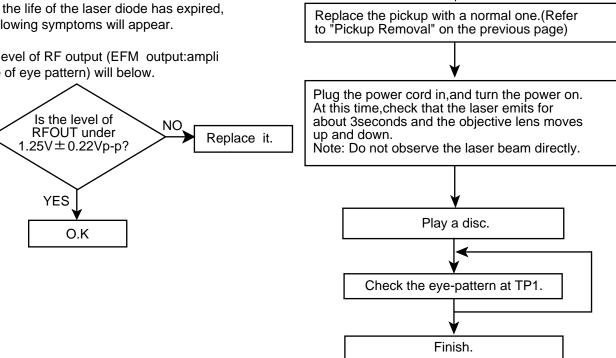

# Maintenance of laser pickup

- (1) Cleaning the pick up lens Before you replace the pick up, please try to clean the lens with a alcohol soaked cotton swab.

- (2) Life of the laser diode When the life of the laser diode has expired, the following symptoms will appear.

- 1. The level of RF output (EFM output:ampli tude of eye pattern) will below.

(3) Semi-fixed resistor on the APC PC board

The semi-fixed resistor on the APC printed circuit board which is attached to the pickup is used to adjust the laser power. Since this adjustment should be performed to match the characteristics of the whole optical block, do not touch the semi-fixed resistor.

If the laser power is lower than the specified value, the laser diode is almost worn out, and the laser pickup should be replaced.

If the semi-fixed resistor is adjusted while the pickup is functioning normally, the laser pickup may be damaged due to excessive current.

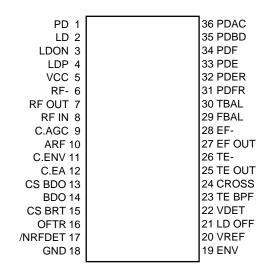

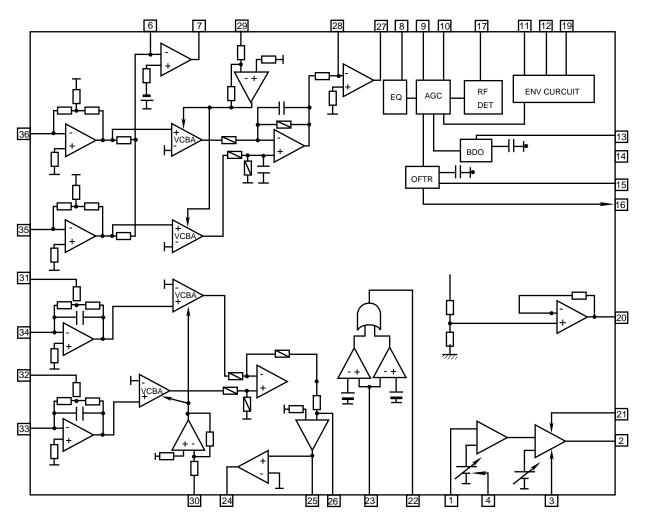

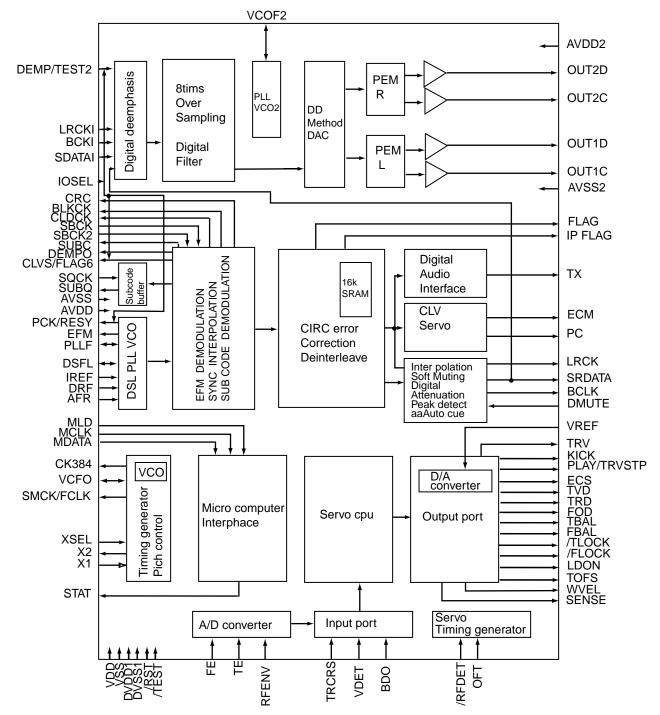

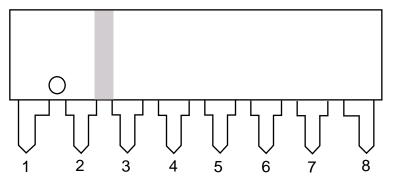

# Description of major ICs ■ AN8806SB-W (IC601) : RF&SERVO AMP

1.Pin layout

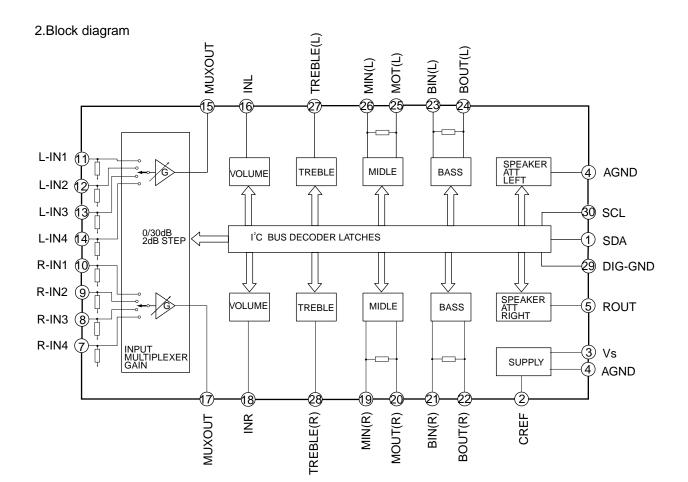

#### 2.Block diagram

#### 3. Pin function

| Pin No. | symbol  | I/O   | Function                                                                |  |  |  |  |  |  |

|---------|---------|-------|-------------------------------------------------------------------------|--|--|--|--|--|--|

| 1       | PD      | Ι     | APC amp . Input terminal                                                |  |  |  |  |  |  |

| 2       | LD      | 0     | APC amp . Output terminal                                               |  |  |  |  |  |  |

| 3       | LD ON   | Ι     | LD ON/OFF control terminal                                              |  |  |  |  |  |  |

| 4       | LDP     |       | Connect to GND                                                          |  |  |  |  |  |  |

| 5       | VCC     |       | Power supply                                                            |  |  |  |  |  |  |

| 6       | RF-     | Ι     | RF amp . Reversing input terminal                                       |  |  |  |  |  |  |

| 7       | RF OUT  | 0     | RFamp . Output terminal                                                 |  |  |  |  |  |  |

| 8       | RF IN   | Ι     | AGC input terminal                                                      |  |  |  |  |  |  |

| 9       | C.AGC   | I/O   | AGC loop filter connection terminal                                     |  |  |  |  |  |  |

| 10      | ARF     | 0     | ARF output terminal                                                     |  |  |  |  |  |  |

| 11      | C.ENV   | I/O   | RF detection capacity connection terminal                               |  |  |  |  |  |  |

| 12      | C.EA    | I/O   | HPF-amp capacity connection terminal                                    |  |  |  |  |  |  |

| 13      | CS BDO  | I/O   | Capacity connection terminal for RF discernment side envelope detection |  |  |  |  |  |  |

| 14      | BDO     | 0     | BDO output terminal                                                     |  |  |  |  |  |  |

| 15      | CS BRT  | I/O   | Capacity connection terminal for RF discernment side envelope detection |  |  |  |  |  |  |

| 16      | OFTR    | 0     | OFTR output terminal                                                    |  |  |  |  |  |  |

| 17      | /NRFDET | 0     | RFDET output terminal                                                   |  |  |  |  |  |  |

| 18      | GND     |       | Connect to GND                                                          |  |  |  |  |  |  |

| 19      | ENV     | 0     | 3TENV output terminal                                                   |  |  |  |  |  |  |

| 20      | VREF    | 0     | VREF output terminal                                                    |  |  |  |  |  |  |

| 21      | LD OFF  |       | APC OFF control terminal                                                |  |  |  |  |  |  |

| 22      | VDET    | 0     | VDET output terminal                                                    |  |  |  |  |  |  |

| 23      | TE BPF  | Ι     | VDET input terminal                                                     |  |  |  |  |  |  |

| 24      | CROSS   | 0     | CROSS output terminal                                                   |  |  |  |  |  |  |

| 25      | TE OUT  | 0     | TE amp . Output terminal                                                |  |  |  |  |  |  |

| 26      | TE-     | Ι     | FE amp . Reversing input terminal                                       |  |  |  |  |  |  |

| 27      | FE OUT  | 0     | FE amp . output terminal                                                |  |  |  |  |  |  |

| 28      | FE-     | Ι     | FE amp . Reversing input terminal                                       |  |  |  |  |  |  |

| 29      | FBAL    | Ι     | F.BAL control terminal                                                  |  |  |  |  |  |  |

| 30      | TBAL    | Ι     | T.BAL control terminal                                                  |  |  |  |  |  |  |

| 31      | PDFR    | I/O   | I-V amp conversion resistance adjustment terminal                       |  |  |  |  |  |  |

| 32      | PDER    | I/O   | I-V amp conversion resistance adjustment terminal                       |  |  |  |  |  |  |

| 33      | PDF     | Ι     | I-V amp input terminal                                                  |  |  |  |  |  |  |

| 34      | PDE     | Ι     | I-V amp input terminal                                                  |  |  |  |  |  |  |

| 35      | PD BD   | Ι     | I-V amp input terminal                                                  |  |  |  |  |  |  |

| 36      | PD AC   | · . · | I-V amp input terminal                                                  |  |  |  |  |  |  |

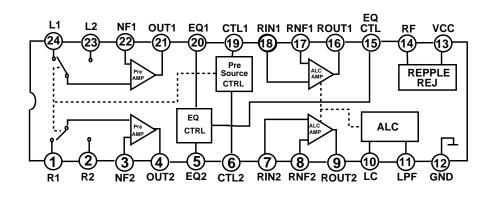

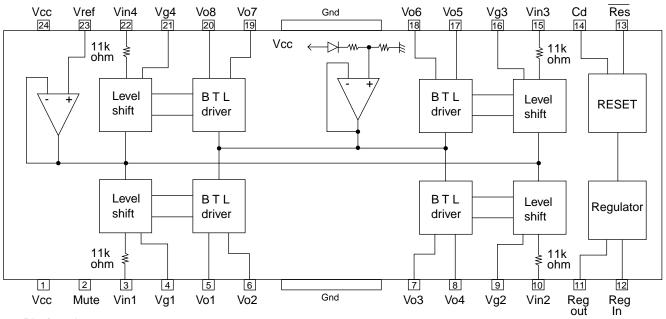

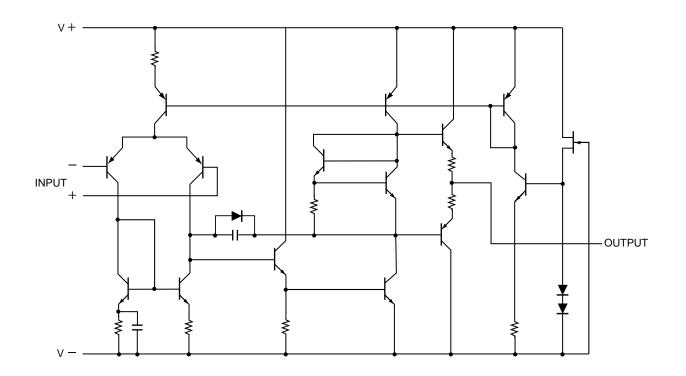

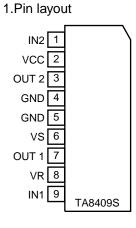

# AN7345 (IC302) : PB/REC AMP

### 1.Block diagram

#### 2. Pin Function

| Pin<br>No. | Symbol | I/O | Function                                      | Pin<br>No. | Symbol | I/O | Function                              |

|------------|--------|-----|-----------------------------------------------|------------|--------|-----|---------------------------------------|

| 1          | R1     | I   | Playback amplifier input                      | 13         | Vcc    | I   | Power supply                          |

| 2          | R2     | I   | Playback amplifier input                      | 14         | RF     | I   | Repple filter                         |

| 3          | NF2    | I   | Playback amplifier negative feedback          | 15         | EQCTL  | Ι   | EQ control                            |

| 4          | OUT2   | 0   | Playback amplifier output                     | 16         | ROUT1  | 0   | Recording amplifier output            |

| 5          | EQ2    | Ι   | Equlaizer                                     | 17         | RNF1   | I   | Recording amplifier negative feedback |

| 6          | CTL2   | I   | Pre Amplifier input swithing time<br>constant | 18         | RIN1   | I   | Recording amplifier input             |

| 7          | RIN2   | I   | Recording amplifier input                     | 19         | CTL1   | I   | Pre amplifier input swithing control  |

| 8          | RNF2   | I   | Recording amplifier negative feedback         | 20         | EQ1    | I   | Equlayzer                             |

| 9          | ROUT2  | 0   | Recording amplifier output                    | 21         | OUT1   | 0   | Playback amplifier output             |

| 10         | LC     | Ι   | ALC low cut                                   | 22         | NF1    | Ι   | Playback amplifier negative feedback  |

| 11         | LPF    | I   | ALC low pass filter                           | 23         | L2     | Ι   | Playback amplifier input              |

| 12         | GND    | Ι   | —                                             | 24         | L1     | Ι   | Playback amplifier input              |

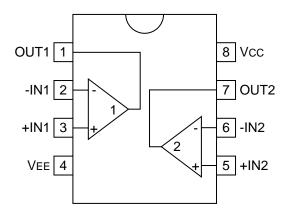

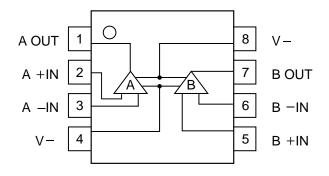

# ■ BA15218 (IC526,481,501,502,571,546) : OP AMP.

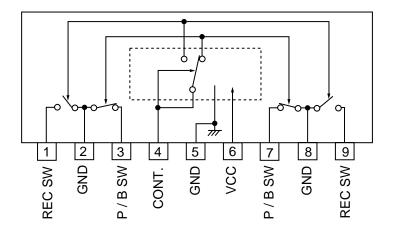

## BA3126N (IC301) : Head SW

1. Terminal layout and Block diagram

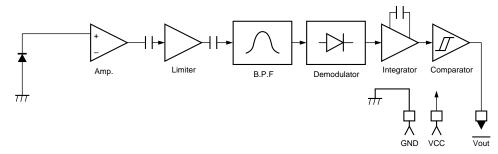

# ■ GP1U281X (IC915) : Receiver for remote controller

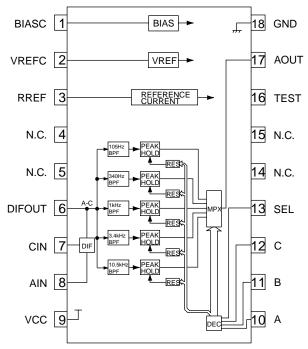

# ■ BA3835S (IC812) : SPI B.P.F.

1.Block Diagrams

### 2.Pin Function

| No. | Symbol | I/O | Function                                              |  |  |  |

|-----|--------|-----|-------------------------------------------------------|--|--|--|

| 1   | BIASC  | -   | Decoupling condenser connection terminal.             |  |  |  |

| 2   | VREFC  | -   | Decoupling condenser connection terminal.             |  |  |  |

| 3   | RPEF   | -   | Reference resistance connection terminal.             |  |  |  |

| 4   | NC     | -   | Non connect.                                          |  |  |  |

| 5   | NC     | -   | Non connect.                                          |  |  |  |

| 6   | NC     | -   | Non connect.                                          |  |  |  |

| 7   | CIN    | -   | Connected to GND of audio system through a condenser. |  |  |  |

| 8   | AIN    | Ι   | Inputs the audio signal through a condenser.          |  |  |  |

| 9   | VCC    | -   | Power supply terminal.                                |  |  |  |

| 10  | SPI-A  | 0   | Output selection control terminal.                    |  |  |  |

| 11  | SPI-B  | 0   | Output selection control terminal.                    |  |  |  |

| 12  | SPI-C  | 0   | Output selection control terminal.                    |  |  |  |

| 13  | SPICSB | 0   | Output selection control terminal.                    |  |  |  |

| 14  | NC     | -   | Non connect.                                          |  |  |  |

| 15  | NC     | -   | Non connect.                                          |  |  |  |

| 16  | TEST   | -   | Connected to GND upon normal use.                     |  |  |  |

| 17  | AOUT   | 0   | Multi-plexor output terminal.                         |  |  |  |

| 18  | GND    | -   | Connect to GND.                                       |  |  |  |

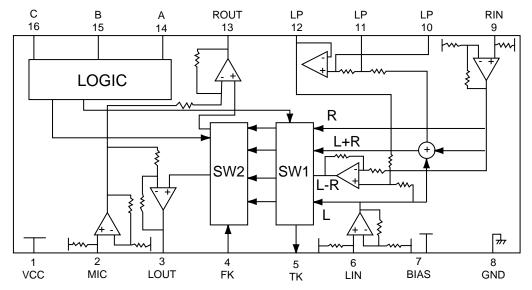

# ■ BA3837 (IC466) : MIC Mixer

### 1.Block diagram

#### 2.Pin function

| Pin No. | Symbol | I/O | Description                           |

|---------|--------|-----|---------------------------------------|

| 1       | VCC    | -   | Power supply                          |

| 2       | MIC IN | I   | Microphone mixing input               |

| 3       | LOUT   | 0   | Channel L output                      |

| 4       | FK     | -   | Non connect                           |

| 5       | TK     | -   | Non connect                           |

| 6       | LIN    |     | Channel L input                       |

| 7       | BIAS   |     | Signal bias                           |

| 8       | GND    | -   | Connect to GND                        |

| 9       | RIN    |     | Channel R input                       |

| 10      | LPF1   | 0   | Connects to LPF time constant element |

| 11      | LPF2   | 0   | Connects to LPF time constant element |

| 12      | LPF3   | 0   | LPF outpout                           |

| 13      | ROUT   | 0   | Channel R output                      |

| 14      | CONTA  |     | Mode select input A                   |

| 15      | CONTB  |     | Mode select input B                   |

| 16      | CONTC  |     | Mode select input C                   |

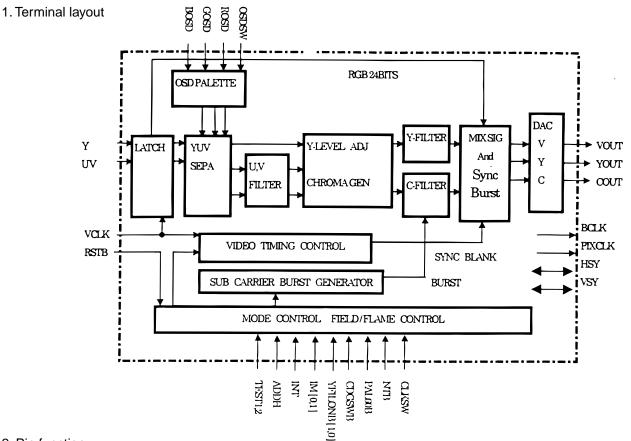

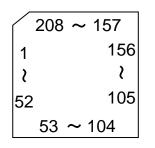

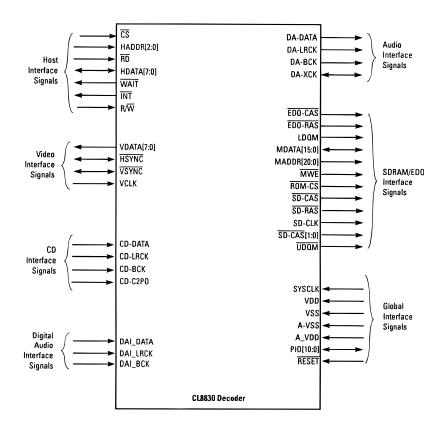

# BU1427K (IC152) : Digital RGB-TV Encoder

#### 2. Pin function

| No. | NAME    | FUNCTION                  | No. | NAME     | FUNCTION                    |

|-----|---------|---------------------------|-----|----------|-----------------------------|

| 1   | BOSD    | OSD BLUE DATA INPUT       | 33  | SLABEB   | SELECT MASTER/SLAVE         |

| 2   | Y0/YUV0 | YUV DATA                  | 34  | ADDH     | +0.5/-0.5 LINE at NON-INTER |

| 3   | Y1/YUV1 | YUV DATA                  | 35  | VREF-C   | DAC BIAS                    |

| 4   | Y2/YUV2 | YUV DATA                  | 36  | CGND     | CHROMA OUTPUT GROUND        |

| 5   | Y3/YUV3 | YUV DATA                  | 37  | COUT     | CHROMA OUTPUT               |

| 6   | Y4/YUV4 | YUV DATA                  | 38  | VGND     | Composite Output Ground     |

| 7   | Y5/YUV5 | YUV DATA                  | 39  | VOUT     | COMPOSITE OUTPUT            |

| 8   | Y6/YUV6 | YUV DATA                  | 40  | AVSS     | Analog Ground (DAC, VREF)   |

| 9   | GND     | DIGITAL GROUND            | 41  | P-VDD    | POWER(DAC) VDD              |

| 10  | Y7/YUV7 | YUV DATA                  | 42  | IR       | REFERENCE RESISTOR          |

| 11  | UV0     | UV DATA                   | 43  | AVDD     | ANALOG (VREF) VDD           |

| 12  | UV1     | UV DATA                   | 44  | YGND     | Luminance Output Ground     |

| 13  | UV2     | UV DATA                   | 45  | YOUT     | Luminance Output            |

| 14  | UV3     | UV DATA                   | 46  | VDD      | DIGITAL VDD                 |

| 15  | OSDSW   | OSD ENABLE/DISABLE        | 47  | YFILON2B | Y-FILSEL THROU/FILON2       |

| 16  | CDGSWB  | SELECT Video CD/CD-G      | 48  | YCOFF    | DAC(YOUT,COUT) OFF          |

| 17  | UV4     | UV DATA                   | 49  | YFILON1B | Y-FILSEL THROU/ FILON1      |

| 18  | UV5     | UV DATA                   | 50  | PAL60B   | NORMAL/PAL60 at PALMODE     |

| 19  | UV6     | UV DATA                   | 51  | VCLK     | Video Clock Input           |

| 20  | UV7     | UV DATA                   | 52  | RSTB     | NORMAL/RESET                |

| 21  | GND     | DIGITAL GROND             | 53  | CLKSW    | SEL*1CLK/*2CLK              |

| 22  | NTB     | SELECT NISC/PAL MODE      | 54  | RD0      | Pull Down to GND            |

| 23  | IM0     | SELECT YUV/YUV            | 55  | RD1      | Pull Down to GND            |

| 24  | IM1     | SELECT DAC/NORMAL         | 56  | RD2      | Pull Down to GND            |

| 25  | TEST1   | Normally pull down to GND | 57  | ROSD     | OSD RED DATA INPUT          |

| 26  | TEST2   | SELECT U/V TIMING         | 58  | RD3      | Pull Down to GND            |

| 27  | VSY     | V-SYNC INPUT or OUTPUT    | 59  | BCLK/RD4 | BASE CLOCK OUT              |

| 28  | HSY     | H-SYNC INPUT or OUTPUT    | 60  | RD5      | Pull Down to GND            |

| 29  | PIXCLK  | 1/2 freq. of BCLK         | 61  | IO VDD   | VDD for I/O                 |

| 30  | VDD     | DIGITAL VDD               | 62  | RD6      | Pull Down to GND            |

| 31  | IO VDD  | VDD for I/O               | 63  | RD7      | Pull Down to GND            |

| 32  | INT     | Interlace /Non-Interlace  | 64  | GOSD     | OSDGREEN DATA INPUT         |

\* The pin built-in pull-down resister. (30kohm)

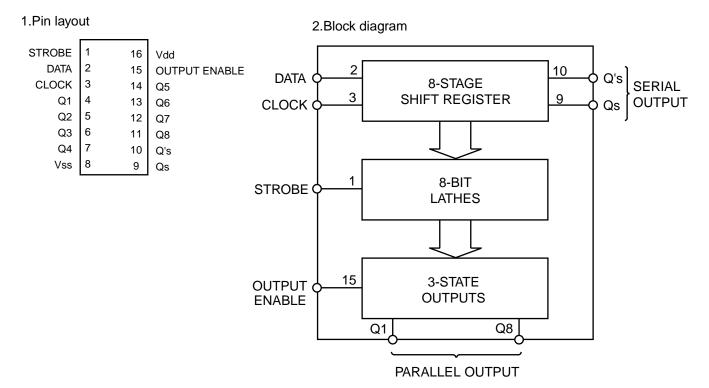

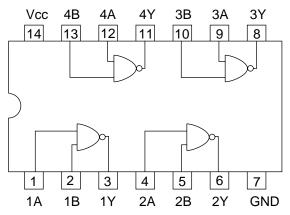

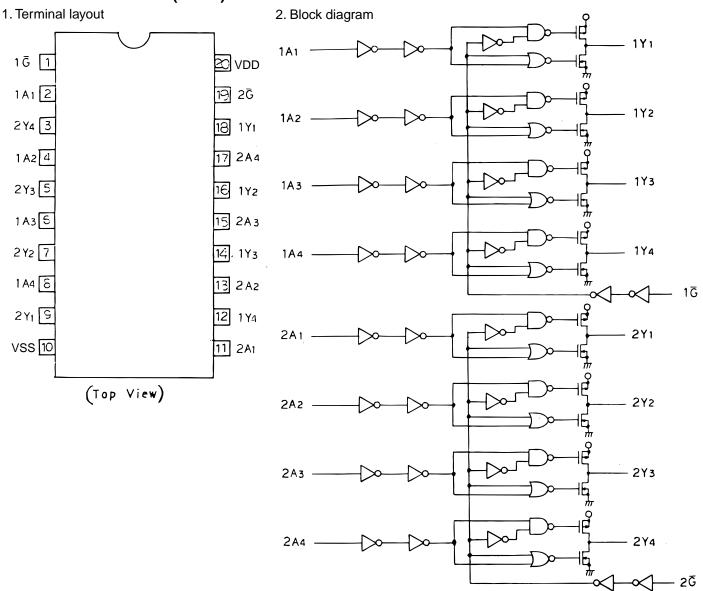

## ■ BU4094BCF (IC303,304,811) : Serial to parallel port extension

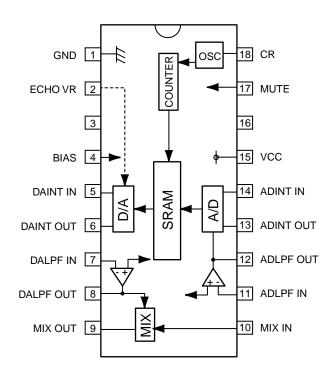

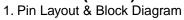

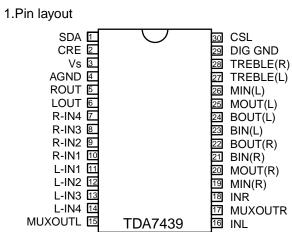

# ■ BU9253AS (IC902) : LPF&ECHO MIX.

1.Pin layout & block diagram

#### 2.Pin function

| Pin No. | Symbol    | I/O | Descriptions                                |

|---------|-----------|-----|---------------------------------------------|

| 1       | GND       | -   | Connect GND                                 |

| 2       | ECHO VR   | l   | Echo level control                          |

| 3       |           | -   | Non connect                                 |

| 4       | BIAS      | -   | Analog part DC bias                         |

| 5       | DAINT IN  |     | DA side integrator input                    |

| 6       | DAINT OUT | 0   | DA side integrator output                   |

| 7       | DALPF IN  | I   | DA side LPF input                           |

| 8       | DALPF OUT | 0   | DAside LPF output                           |

| 9       | MIX OUT   | 0   | Mix AMP output for original tone& echo tone |

| 10      | MIX IN    |     | Mix AMP input pin for original tone         |

| 11      | ADLPF IN  |     | AD side LPF input                           |

| 12      | ADLPF OUT | 0   | AD side LPF output                          |

| 13      | ADINT OUT | 0   | AD side integrator output                   |

| 14      | ADINT IN  |     | AD side integrator input                    |

| 15      | VCC       | -   | Power supply                                |

| 16      | NC2       | -   | Non connect                                 |

| 17      | MUTE      |     | Mute control signal input                   |

| 18      | CR        | -   | CR pin for oscillator                       |

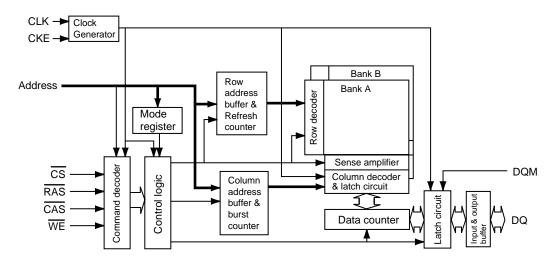

# ■ HY57V161610DTC8 or KM416S1120DT-G8 (IC104) : 16MB SDRAM

1.Block diagram

#### 2.Pin function

| Pin No. | Symbol | Description           | Pin No. | Symbol  | Description          |

|---------|--------|-----------------------|---------|---------|----------------------|

| 1       | VCC    | Power supply          | 26      | VSS     | Connect to GND       |

| 2,3     | DQ0,1  | Data input/output     | 27~32   | A4~9    | Address inputs       |

| 4       | VSS    | Connect to GND        | 33      | NC      | Non connect          |

| 5,6     | DQ2,3  | Data input/output     | 34      | CKE     | Clock enable         |

| 7       | VDD    | Power supply          | 35      | CLK     | System clock input   |

| 8,9     | DQ4,5  | Data input/output     | 36      | UDQM    | Upper DQ mask enable |

| 10      | VSS    | Connect to GND        | 37      | NC      | Non connect          |

| 11,12   | DQ6,7  | Data input/output     | 38      | VCC     | Power supply         |

| 13      | VCC    | Power supply          | 39,40   | DQ8,9   | Data input/output    |

| 14      | LDQM   | Lower DQ mask enable  | 41      | VSS     | Connect to GND       |

| 15      | WE     | Write enable          | 42,43   | DQ10,11 | Data input/output    |

| 16      | CAS    | Column address strobe | 44      | VDD     | Power supply         |

| 17      | RAS    | Row address strobe    | 45,46   | DQ12,13 | Data input/output    |

| 18      | CS     | Chip enable           | 47      | VSS     | Connect to GND       |

| 19,20   | A11,10 | Address inputs        | 48,49   | DQ14,15 | Data input/output    |

| 21~24   | A0~3   | Address inputs        | 50      | VSS     | Connect to GND       |

| 25      | VCC    | Power supply          |         |         |                      |

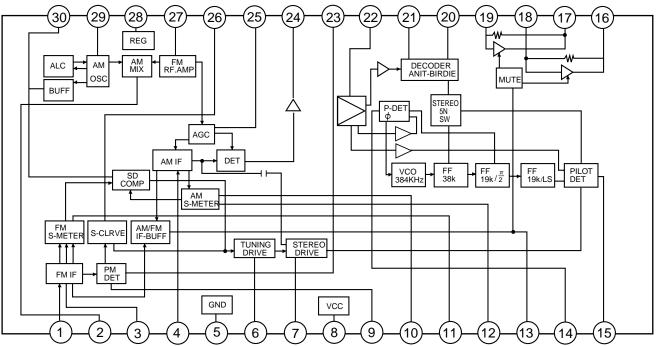

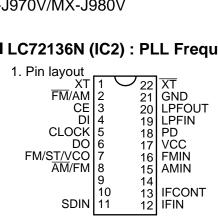

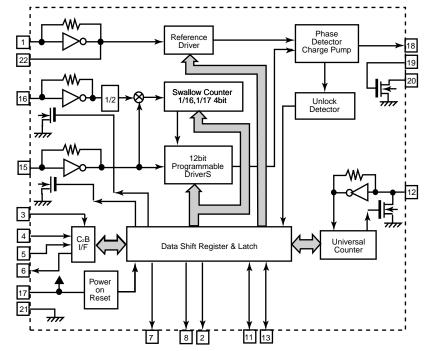

# ■ LA1838 (IC1) : FM AM IF AMP&detector, FM MPX Decoder

1. Block Diagram

#### 2. Pin Function

| Pin<br>No. | Symbol  | I/O | Function                                                                                                          | Pin<br>No. | Symbol     | I/O | Function                                                                                       |

|------------|---------|-----|-------------------------------------------------------------------------------------------------------------------|------------|------------|-----|------------------------------------------------------------------------------------------------|

| 1          | FM IN   | Ι   | This is an input terminal of FM IF signal.                                                                        | 16         | R OUT      | 0   | Right channel signal output.                                                                   |

| 2          | AM MIX  | 0   | This is an out put terminal for AM mixer.                                                                         | 17         | L OUT      | 0   | Left channel signal output.                                                                    |

| 3          | FM IF   | I   | Bypass of FM IF                                                                                                   | 18         | R IN       | I   | Input terminal of the Right channel post AMP.                                                  |

| 4          | AM IF   | Ι   | Input of AM IF Signal.                                                                                            | 19         | L IN       | Ι   | Input terminal of the Left channel post AMP.                                                   |

| 5          | GND     | Ι   | This is the device ground terminal.                                                                               | 20         | RO         | 0   | Mpx Right channel signal output.                                                               |

| 6          | TUNED   | 0   | When the set is tunning,this terminal becomes "L".                                                                | 21         | LO         | 0   | Mpx Left channel signal output.                                                                |

| 7          | STEREO  | 0   | Stereo indicator output. Stereo "L",<br>Mono: "H"                                                                 | 22         | IF IN      | I   | Mpx input terminal                                                                             |

| 8          | VCC     | -   | This is the power supply terminal.                                                                                | 23         | FM OUT     | 0   | FM detection output.                                                                           |

| 9          | FM DET  | -   | FM detect transformer.                                                                                            | 24         | AM DET     | 0   | AM detection output.                                                                           |

| 10         | AM SD   | I   | This is a terminal of AM ceramic filter.                                                                          | 25         | AM AGC     | Ι   | This is an AGC voltage input terminal for AM                                                   |

| 11         | FM VSM  | 0   | Adjust FM SD sensitivity.                                                                                         | 26         | AFC        | -   | This is an output terminal of voltage for FM-AFC.                                              |

| 12         | AM VSM  | 0   | Adjust AM SD sensitivity.                                                                                         | 27         | AM RF      | Ι   | AM RF signal input.                                                                            |

| 13         | MUTE    | I/O | When the signal of IF REQ of IC121(<br>LC72131) appear, the signal of FM/AM<br>IF output. //Muting control input. | 28         | REG        | 0   | Register value between pin 26 and pin28<br>besides the frequency width of the<br>input signal. |

| 14         | FM/AM   | Ι   | Change over the FM/AM input.<br>"H" :FM, "L" : AM                                                                 | 29         | AM OSC     | _   | This is a terminal of AM Local oscillation circuit.                                            |

| 15         | MONO/ST | 0   | Stereo : "H", Mono: "L"                                                                                           | 30         | OSC BUFFER | 0   | AM Local oscillation Signal output.                                                            |